TSMC described its subsequent era transistor know-how this week on the IEEE International Electron Device Meeting (IEDM) in San Francisco. The N2, or 2-nanometer, know-how is the semiconductor foundry big’s first foray into a brand new transistor structure, referred to as nanosheet or gate-all-around.

Samsung has a course of for manufacturing related units, and each Intel and TSMC count on to be producing them in 2025.

In comparison with TSMC’s most superior course of at the moment, N3 (3-nanometer), the brand new know-how provides as much as a 15 % velocity up or as a lot as 30 % higher vitality effectivity, whereas growing density by 15 %.

N2 is “the fruit of greater than 4 years of labor,” Geoffrey Yeap, TSMC vice chairman of R&D and superior know-how instructed engineers at IEDM. Immediately’s transistor, the FinFET, has a vertical fin of silicon at its coronary heart. Nanosheet or gate-all-around transistors have a stack of slim ribbons of silicon as an alternative.

The distinction not solely gives higher management of the movement of present by means of the machine, it additionally permits engineers to provide a bigger number of units, by making wider or narrower nanosheets. FinFETs may solely present that selection by multiplying the variety of fins in a tool—reminiscent of a tool with one or two or three fins. However nanosheets give designers the choice of gradations in between these, such because the equal of 1.5 fins or no matter would possibly go well with a selected logic circuit higher.

Known as Nanoflex, TSMC’s tech permits completely different logic cells constructed with completely different nanosheetwidths on the identical chip. Logic cells constructed from slim units would possibly make up normal logic on the chip, whereas these with broader nanosheets, able to driving extra present and switching sooner, would make up the CPU cores.

The nanosheet’s flexibility has a very giant influence on SRAM, a processor’s predominant on-chip reminiscence. For a number of generations, this key circuit, made up of 6 transistors, has not been shrinking as quick as different logic. However N2 appears to have damaged this streak of scaling stagnation, leading to what Yeap described because the densest SRAM cell up to now: 38 megabits per sq. millimeter, or an 11 % increase over the earlier know-how, N3. N3 solely managed a 6 % increase over its personal predecessor. “SRAM harvests the intrinsic acquire of going to gate-all-around,” says Yeap.

Future Gate-All-Round Transistors

Whereas TSMC delivered particulars of subsequent 12 months’s transistor, Intel checked out how lengthy trade would possibly be capable to scale it down. Intel’s reply: Longer than initially thought.

“The nanosheet structure truly is the ultimate frontier of transistor structure,” Ashish Agrawal, a silicon technologist in Intel’s parts analysis group, instructed engineers. Even future complementary FET (CFET) units, probably arriving within the mid-2030s, are constructed of nanosheets. So it’s vital that researchers perceive their limits, stated Agrawal.

“Now we have not hit a wall. It’s doable, and right here’s the proof… We’re making a very fairly good transistor.” —Sanjay Natarajan, Intel

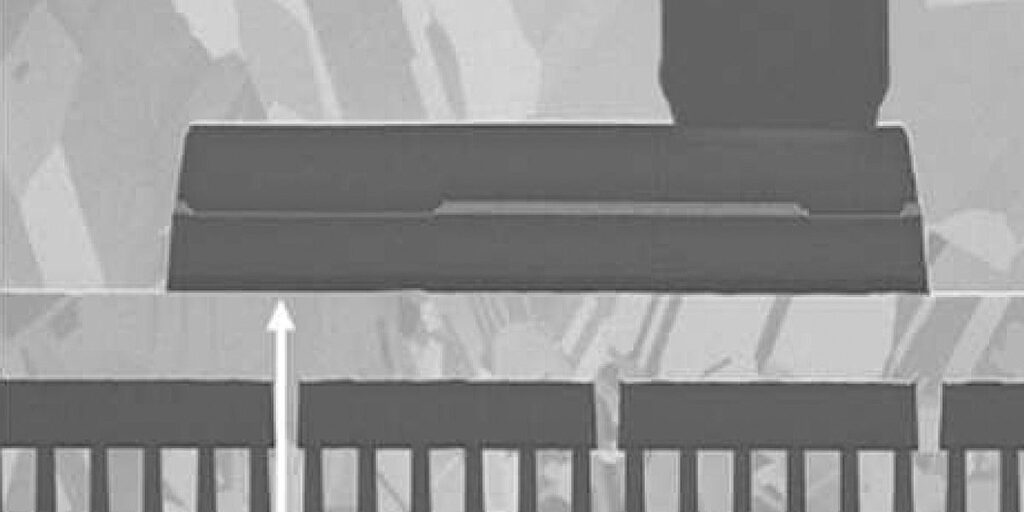

Intel proved {that a} transistor with a 6-nanometer gate size works nicely.Intel

Intel explored a essential scaling issue, gate size, which is the gap lined by the gate between the transistor’s supply and drain. The gate controls the movement of present by means of the machine. Cutting down gate size is essential to decreasing the minimal distance from machine to machine inside normal logic circuits, referred to as referred to as contacted poly pitch, or CPP, for historic causes.

“CPP scaling is primarily by gate size, however it’s predicted this can stall on the 10-nanometer gate size,” stated Agrawal. The considering had been that 10 nanometers was such a brief gate size that, amongst different issues, an excessive amount of present would leak throughout the machine when it was speculated to be off.

“So we checked out pushing beneath 10 nanometers,” Agrawal stated. Intel modified the standard gate-all-around construction so the machine would have solely a single nanosheet by means of which present would movement when the machine was on.

By thinning that nanosheet down and modifying the supplies surrounding it, the workforce managed to provide an acceptably performing machine with a gate size of simply 6 nm and a nanosheet simply 3 nm thick.

Ultimately, researchers count on silicon gate-all-around units to achieve a scaling restrict, so researchers at Intel and elsewhere have been working to exchange the silicon within the nanosheet with 2D semiconductors reminiscent of molybdenum disulfide. However the 6-nanometer outcome means these 2D semiconductors may not be wanted for some time.

“Now we have not hit a wall,” says Sanjay Natarajan, senior vice chairman and normal supervisor of know-how analysis at Intel Foundry. “It’s doable, and right here’s the proof… We’re making a very fairly good transistor” on the 6-nanometer channel size.

From Your Web site Articles

Associated Articles Across the Net